# A 500kHz - 5MHz CW Stepped Frequency Borehole Tomographic Imaging System

### Adam Rhett Isaacson

A dissertation submitted to the Department of Electrical Engineering,

University of Cape Town, in fulfilment of the requirements

for the degree of Master of Science in Engineering.

Cape Town, December 2002

# Declaration

| I declare that this dissertation is my own, unaided work. It is being submitted for<br>the degree of Master of Science in Engineering in the University of Cape Town. It |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| has not been submitted before for any degree or examination in any other university                                                                                      |

|                                                                                                                                                                          |

|                                                                                                                                                                          |

|                                                                                                                                                                          |

|                                                                                                                                                                          |

|                                                                                                                                                                          |

| Signature of Author                                                                                                                                                      |

|                                                                                                                                                                          |

|                                                                                                                                                                          |

| С Т                                                                                                                                                                      |

| Cape Town                                                                                                                                                                |

| 1 December 2002                                                                                                                                                          |

# Abstract

Professor Iain Mason, of the University of Sydney, De Beers, and Reutech Radar Systems sponsored the Radar Remote Sensing Group at UCT to develop a prototype, CW, Stepped Frequency, Borehole, Tomographic Imaging System, proposed by Dr. Alan Langman, of the University of Cape Town. The system is to demonstrate that a coherent system can be achieved using DDS technology.

This dissertation involves a study of Cross-Borehole Tomography. The mathematical physical models of the Radon Transform are reviewed. The entire Cross-Borehole Tomographic process is simulated, based on these physical models of the Radon Transform. The system specifications for the final design are based on the results from the simulation. Finally, the final design is built, and tested.

The phase yields a better quality of image reconstruction when compared to amplitude, and hence a coherent system is a good choice. The system is frequency to frequency coherent for the entire transmit frequency range, which satisfies the main aim of this dissertation.

# Acknowledgements

I would like to thank the following people who helped bring about this dissertation:

- My supervisor, Professor M. R. Inggs, for his help, assistance, and valued support during this dissertation.

- Dr. Alan Langman, for his enthusiasm, moral support, and his many suggestions during this dissertation.

- Professor Iain Mason, for his financial support, and interest in this dissertation.

- De Beers for their financial support.

- Reutech Radar Systems, for their financial support, and use of their facilities during this dissertation. A special mention to Chris May, Bryn Jones, Pieter-Jan Wolfaardt, Paul Fourie, PW van der Walt, and Sven Holfelder. Thanks guys, your support was most appreciated!

- Finally, I would like to thank my mom, and my girlfriend, Gina, for their moral support. Love you both!

# Contents

| D            | eclar                | ation   |                                       | i    |

|--------------|----------------------|---------|---------------------------------------|------|

| $\mathbf{A}$ | bstra                | ct      |                                       | ii   |

| A            | ckno                 | wledge  | ements                                | iv   |

| Li           | st of                | Symb    | ols                                   | xii  |

| N            | omer                 | ıclatur | ·e                                    | xiii |

| 1            | Intr                 | oduct   | ion                                   | 1    |

|              | 1.1                  | Backg   | round                                 | . 1  |

|              | 1.2                  | Outlir  | ne of dissertation                    | . 2  |

|              |                      | 1.2.1   | Introduction                          | . 2  |

|              |                      | 1.2.2   | Cross-Borehole Tomography             | . 2  |

|              |                      | 1.2.3   | Physical Model of the Radon Transform | . 3  |

|              |                      | 1.2.4   | Simulation                            | . 4  |

|              |                      | 1.2.5   | Final Design                          | . 4  |

|              |                      | 1.2.6   | Design and Test Analysis              | . 6  |

|              |                      | 1.2.7   | Conclusions and Recommendations       | . 7  |

| <b>2</b>     | $\operatorname{Cro}$ | ss-Bor  | rehole Tomography                     | 10   |

|   | 2.1 | Introduction                                  | 10 |  |

|---|-----|-----------------------------------------------|----|--|

|   | 2.2 | Cross-Borehole Electromagnetic Imaging        | 10 |  |

|   | 2.3 | Environmental Factors                         | 11 |  |

|   | 2.4 | Image Reconstruction Techniques               | 12 |  |

|   |     | 2.4.1 Projection-Slice Theorem                | 13 |  |

|   |     | 2.4.2 Backprojection                          | 14 |  |

|   |     | 2.4.3 Iterative Methods                       | 14 |  |

|   | 2.5 | Conclusion                                    | 15 |  |

| 3 | Phy | sical Model of the Radon Transform            | 16 |  |

|   | 3.1 | Introduction                                  | 16 |  |

|   | 3.2 | Continuous Case                               | 17 |  |

|   | 3.3 | Discrete Case                                 | 19 |  |

|   | 3.4 | Conclusion                                    | 26 |  |

| 4 | Sim | nulation 2                                    |    |  |

|   | 4.1 | Introduction                                  | 27 |  |

|   | 4.2 | Tomographic Simulation                        | 27 |  |

|   | 4.3 | ADC Resolution                                | 32 |  |

|   | 4.4 | Tomographic Resolution                        | 33 |  |

|   | 4.5 | LNA Gain                                      | 35 |  |

|   | 4.6 | Frequency Step Size                           | 36 |  |

|   | 4.7 | Phase vs Amplitude                            | 39 |  |

|   |     | 4.7.1 Phase and Amplitude Extraction          | 39 |  |

|   |     | 4.7.2 Attenuation and Velocity Reconstruction | 42 |  |

|   |     | 4.7.2 Recentation and velocity reconstruction | 74 |  |

| 5 | Fina | al Desi | ${f gn}$                                           | 51 |

|---|------|---------|----------------------------------------------------|----|

|   | 5.1  | Introd  | uction                                             | 51 |

|   | 5.2  | Propos  | sed Architectures                                  | 51 |

|   |      | 5.2.1   | RF Sampling                                        | 52 |

|   |      | 5.2.2   | Homodyne                                           | 52 |

|   |      | 5.2.3   | Heterodyne                                         | 54 |

|   | 5.3  | System  | n Specifications                                   | 56 |

|   |      | 5.3.1   | IF Band and Transmit Bandwidth                     | 56 |

|   |      | 5.3.2   | Frequency Step Size and Receiver Bandwidth         | 57 |

|   |      | 5.3.3   | LNA Gain                                           | 57 |

|   |      | 5.3.4   | System Clocking                                    | 60 |

|   |      | 5.3.5   | Transmit Power                                     | 61 |

|   |      | 5.3.6   | ADC Dynamic Range, Resolution and Full-Scale Value | 61 |

|   |      | 5.3.7   | Receiver Dynamic Range                             | 61 |

|   |      | 5.3.8   | Receiver Sensitivity                               | 63 |

|   |      | 5.3.9   | Power Consumption                                  | 63 |

|   |      | 5.3.10  | Temperature Range                                  | 64 |

|   |      | 5.3.11  | Board Dimensions                                   | 64 |

|   | 5.4  | Hardw   | are and Software Implementation                    | 65 |

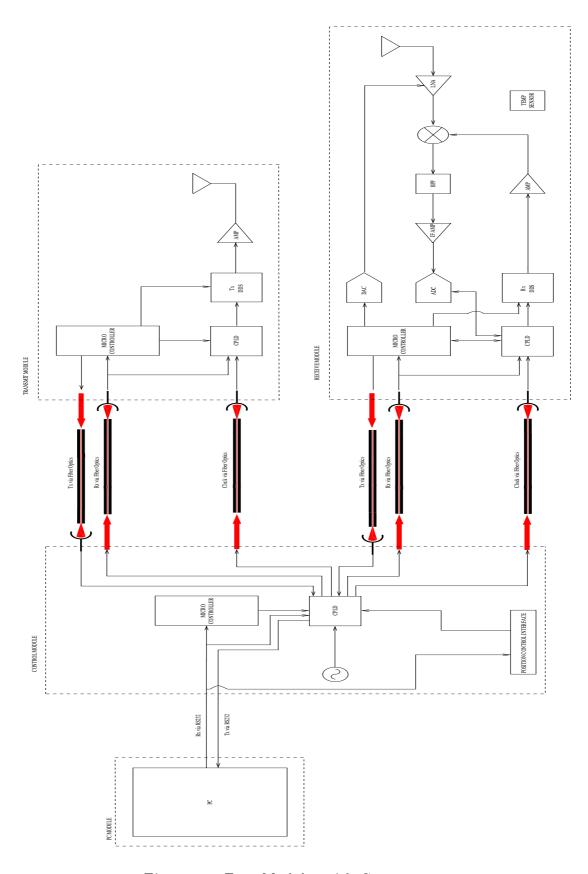

|   |      | 5.4.1   | Control Module                                     | 65 |

|   |      | 5.4.2   | Transmit Module                                    | 70 |

|   |      | 5.4.3   | Receive Module                                     | 72 |

|   |      | 5.4.4   | PC Module                                          | 74 |

|   | 5.5  | Cohere  | ent Control                                        | 78 |

|   |      | 5 5 1   | Start Up Procedure                                 | 78 |

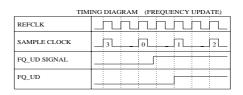

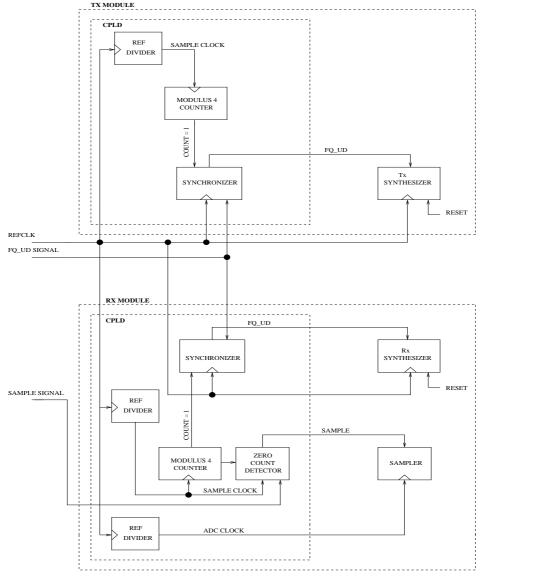

|              |       | 5.5.2 Frequency Updating     | 79          |

|--------------|-------|------------------------------|-------------|

|              |       | 5.5.3 Sampling Process       | 80          |

|              | 5.6   | Conclusion                   | 80          |

| 6            | Des   | ign and Test Analysis        | 83          |

|              | 6.1   | Introduction                 | 83          |

|              | 6.2   | Receiver Dynamic Range       | 84          |

|              | 6.3   | Transmitter Power            | 85          |

|              | 6.4   | LNA Gain                     | 86          |

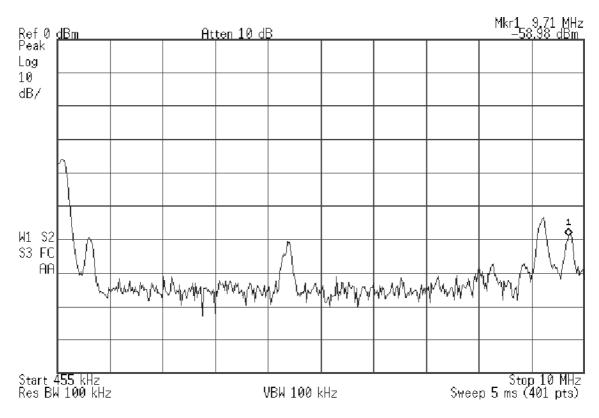

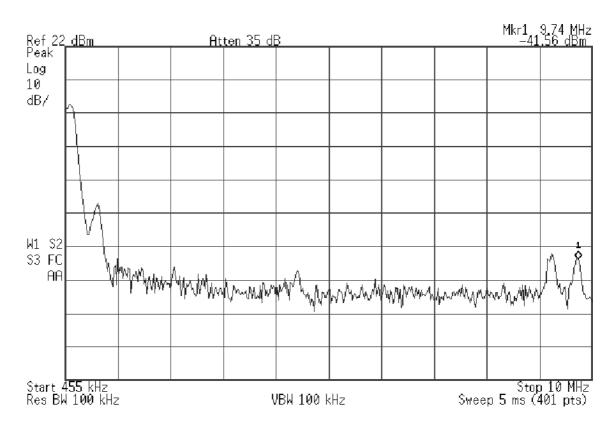

|              | 6.5   | BPF and ADC Harmonics        | 87          |

|              | 6.6   | System Coherency             | 88          |

|              | 6.7   | Conclusion                   | 91          |

| 7            | Con   | clusions and Recommendations | 92          |

|              | 7.1   | Conclusions                  | 92          |

|              | 7.2   | Recommendations              | 94          |

| Bi           | bliog | graphy                       | 99          |

| $\mathbf{A}$ | Sch   | ematics 1                    | 100         |

| В            | Mat   | tlab Simulation              | L <b>04</b> |

| $\mathbf{C}$ | Soft  | ware Flow Diagrams           | L06         |

# List of Figures

| 2.1  | The Cross-Borehole Technique with Dimensions                             | 11 |

|------|--------------------------------------------------------------------------|----|

| 3.1  | Definition of Medium                                                     | 20 |

| 3.2  | Definition of Media                                                      | 21 |

| 3.3  | Continuous Propagation of the E-Field                                    | 22 |

| 3.4  | Discrete Propagation of the E-Field                                      | 22 |

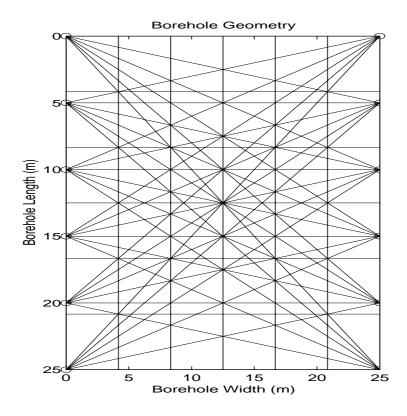

| 4.1  | A Typical Borehole Geometry                                              | 29 |

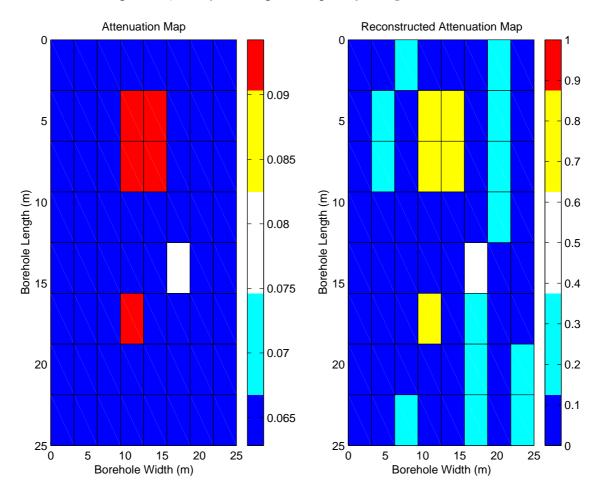

| 4.2  | Simulated and Reconstructed Attenuation Map ( $SNR=67.78\mathrm{dB}$ )   | 30 |

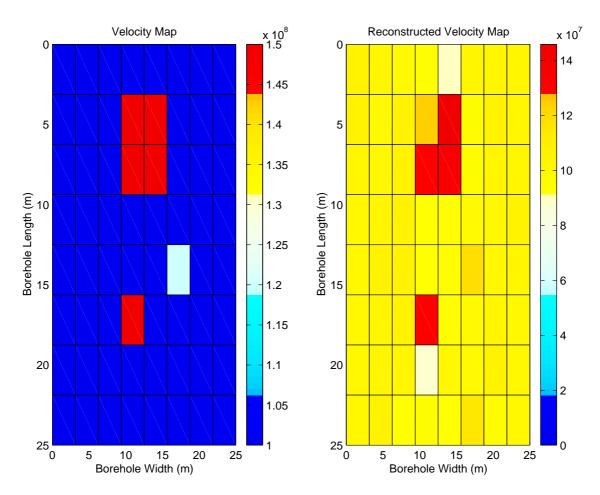

| 4.3  | Simulated and Reconstructed Velocity Map (SNR = 67.78dB)                 | 31 |

| 4.4  | Borehole Geometry with Tx, and Rx Positions $=4$                         | 34 |

| 4.5  | Borehole Geometry with Tx, and Rx Positions $= 6$                        | 35 |

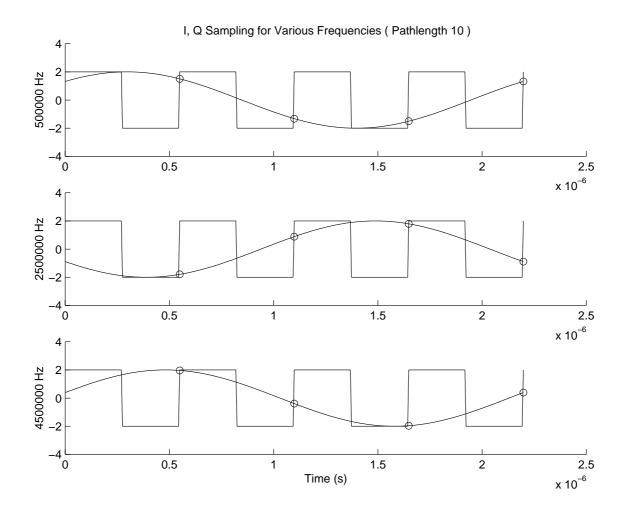

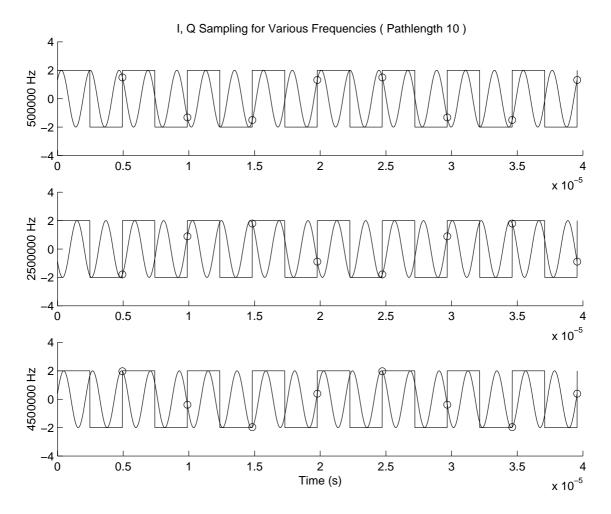

| 4.6  | The Sampling Process (4xIF = 1.82MHz) $\dots \dots \dots$                | 40 |

| 4.7  | The Sampling Process (Under Sampling = $202.222kHz$ )                    | 41 |

| 4.8  | Simulated and Reconstructed Attenuation Map ( $SNR=47.78\mathrm{dB}$ ) . | 43 |

| 4.9  | Simulated and Reconstructed Velocity Map ( $SNR=47.78\mathrm{dB}$ )      | 45 |

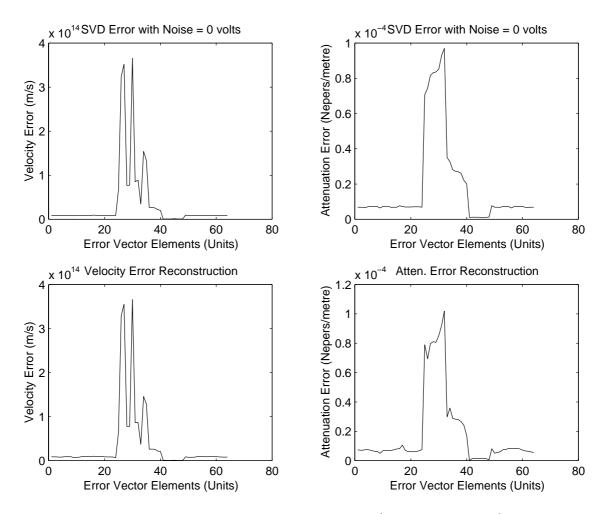

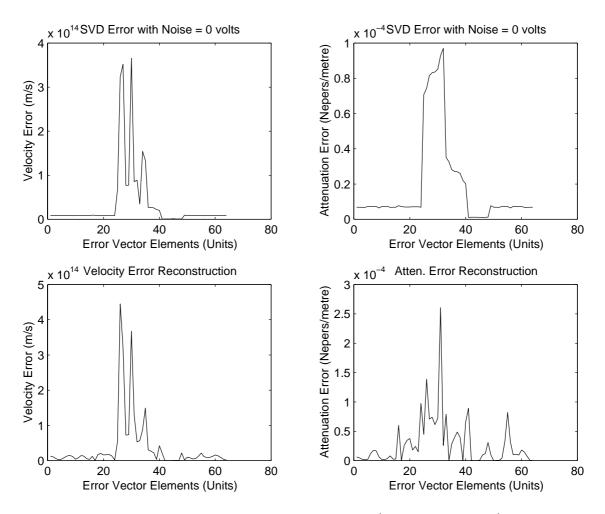

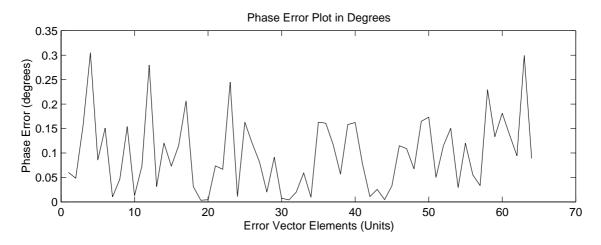

| 4.10 | SVD Reconstruction Error ( $SNR=67.78 \text{dB}$ )                       | 46 |

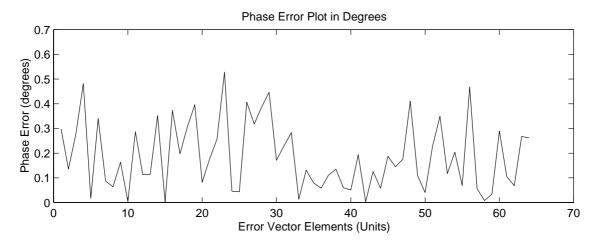

| 4.11 | SVD Reconstruction Error ( $SNR = 47.78$ dB)                             | 47 |

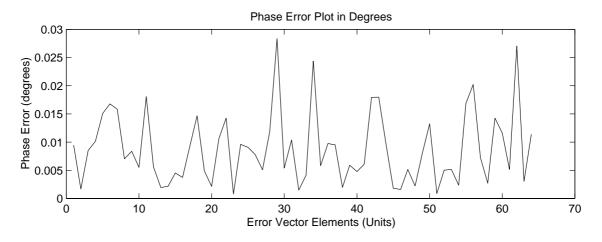

| 4.12 | Phase Error ( $SNR=67.78 	ext{dB}$ )                                     | 48 |

| 4.13 | Phase Error $(SNR = 47.78dB)$                                            | 48 |

| 4.14 | Simulated and Reconstructed Velocity Map $(SNR = 42.68dB)$              | 49  |

|------|-------------------------------------------------------------------------|-----|

| 4.15 | Phase Error $(SNR=42.68	ext{dB})$                                       | 49  |

| 5.1  | RF Sampling Architecture                                                | 53  |

| 5.2  | Homodyne Architecture                                                   | 53  |

| 5.3  | Heterodyne Architecture                                                 | 55  |

| 5.4  | Harmonics Closest to the IF Band of Interest ( $\triangle f = 150kHz$ ) | 58  |

| 5.5  | Harmonics Closest to the IF Band of Interest ( $\triangle f = 455kHz$ ) | 59  |

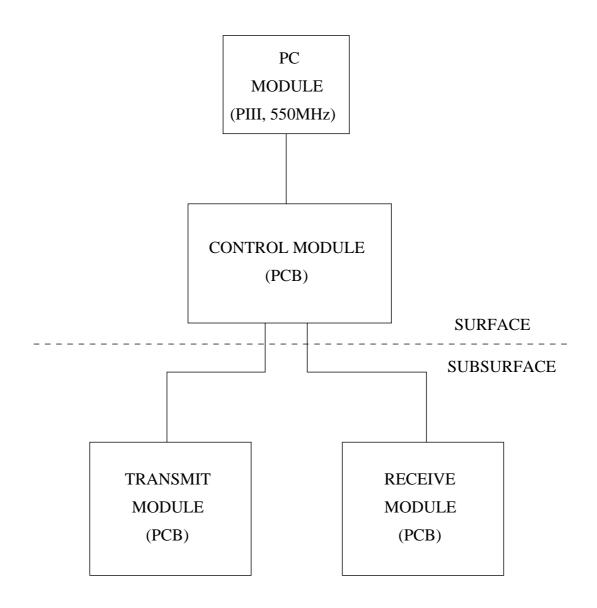

| 5.6  | The Four Modules                                                        | 66  |

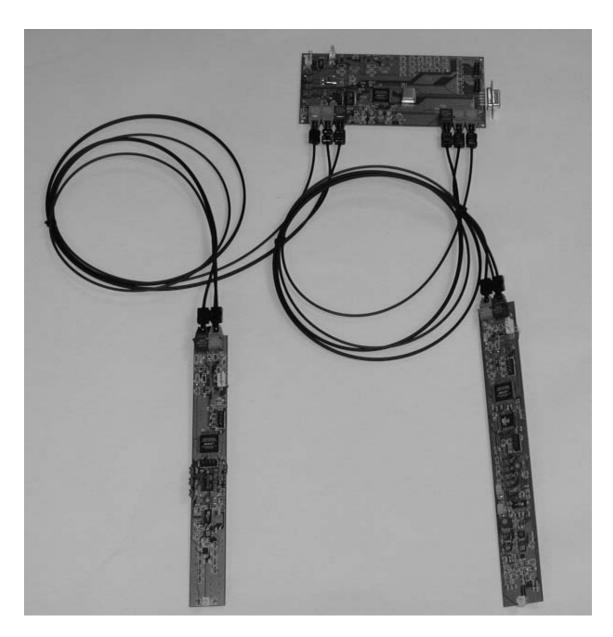

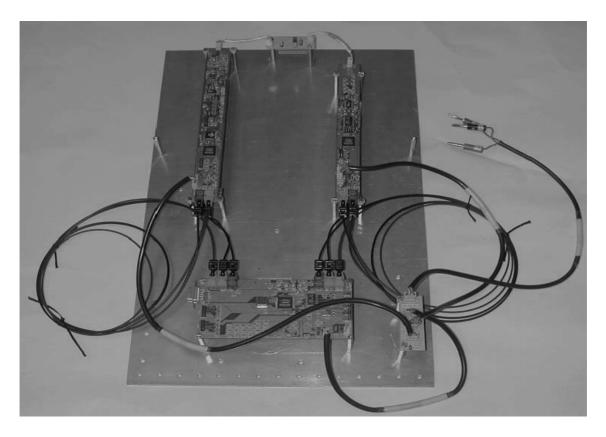

| 5.7  | Final PCB Hardware System                                               | 67  |

| 5.8  | Four Modules with Components                                            | 68  |

| 5.9  | Coherent Control                                                        | 81  |

| 6.1  | Test Setup                                                              | 84  |

| 6.2  | Output BPF Harmonics                                                    | 88  |

| 6.3  | Input ADC Harmonics                                                     | 89  |

| A.1  | Control Module Schematic                                                | 101 |

| A.2  | Transmit Module Schematic                                               | 102 |

| A.3  | Receive Module Schematic                                                | 103 |

| В.1  | Simulation Flow Diagram                                                 | 105 |

| C.1  | Control Module Flow Diagram                                             | 107 |

| C.2  | Transmit Module Flow Diagram                                            | 108 |

| C.3  | Receive Module Flow Diagram                                             | 109 |

| C.4  | Graphical User Interface Flow Diagram                                   | 110 |

| C.5  | Serial Event Listener Flow Diagram                                      | 111 |

# List of Tables

| 4.1 | User Input Typical Values                          | 28 |

|-----|----------------------------------------------------|----|

| 4.2 | Return Values vs LNA Gain (1-32 Ray Path Lengths)  | 37 |

| 4.3 | Return Values vs LNA Gain (33-64 Ray Path Lengths) | 38 |

| 5.1 | Homodyne Mixer Output Harmonics                    | 54 |

| 5.2 | Heterodyne Mixer Output Harmonics (Lower Sideband) | 55 |

| 5.3 | Maximum Power Consumption                          | 64 |

| 5.4 | Board Dimensions                                   | 65 |

| 6.1 | Measured Transmitter Power Values                  | 86 |

| 6.2 | LNA Gain Measured, and Programmed Values           | 87 |

| 6.3 | Frequency to Frequency Coherency Test Results      | 91 |

# List of Symbols

```

A_{pq}

Amplitude of signal along ray path pq.

Speed of light.

c

d_i

Amplitude or traveltime for the ith ray path.

E_{pq}

Electric field of the EM wave along ray path pq.

E_o

Initial electric field constant.

f

— Transmit frequency.

k

Angular wave number.

— Length of the ith ray that passes the jth pixel.

l_{ii}

L_{unambig}

— Unambiguous path length.

N

Number of bits of the ADC.

Attenuation or the velocity for the pixel j.

p_j

P_{1dB}

1dB compression point of the LNA.

Minimum detectable signal within the receiver bandwidth.

P_{min}

T_{pq}

Traveltime along ray path pq.

Velocity of travelling wave.

v

X_m

Full-scale amplitude of the ADC.

Attenuation constant.

\alpha

β

Phase constant.

\Delta f

Frequency step size.

Change in phase.

\Delta \phi

Relative permittivity.

\epsilon_r

Real part of permittivity.

— Imaginary part of permittivity.

Wavelength.

\lambda

Permeability.

\mu

Conductivity.

\sigma

RMS amplitude value of the input ADC signal.

\sigma_x

Angular frequency.

\omega

```

## Nomenclature

Coherent System—A system where the phase information is preserved.

**CW**—Continuous Wave.

IF—Intermediate Frequency.

**BPF**—Band Pass Filter.

**ADC**—Analogue-to-Digital Converter.

**COTS**—Commercial off the Shelf.

**DDS**—Direct Digital Synthesiser.

Cross Borehole Tomography—A process which uses a transmitter, and a receiver in each borehole in order to obtain an image of the subsurface between the two boreholes.

EM Wave—Electromagnetic Wave.

Relative Permittivity—The ratio of the electric displacement in a medium to that which would be produced in free space by the same field.

**Bakelite**—A synthetic resin made by condensation of cresol or phenol with formaldehyde.

Magnetic Permeability—The ratio of flux density to magnetising force.

Conductivity—Reciprocol of the resistivity.

**Homogenous Medium**—The characteristics of the medium remain the same, and do not depend on position.

SVD—Singular Value Decomposition.

LSQ Error—Least Squares Error.

**SNR**—Signal-to-Noise Ratio.

**LNA**—Low Noise Amplifier.

IF Sampling Algorithm—This algorithm extracts the phase from the IF signal by using four IF samples to generate the I, and Q values, and hence the phase can be calculated.

**Quantization Error**—This is the error associated with the ADC. The ADC is essentially a quantizer, which transforms the actual sample values into a set of prescribed values. The difference between the prescribed values, and the actual sample values represents the quantization error.

**PCB**—Printed Circuit Board.

**Flicker Noise**—This is also called pink noise. It is defined as having a  $\frac{1}{f}$  spectrum.

Baud Rate—The number of clock periods per second.

**CPLD**—Complex Programmable Logic Device.

**UART**—Universal Asynchronous Receiver Transmitter.

**PC**—Personal Computer.

**DAC**—Digital-to-Analogue Converter.

# Chapter 1

## Introduction

## 1.1 Background

Professor Iain Mason, of the University of Sydney, De Beers, and Reutech Radar Systems sponsored the Radar Remote Sensing Group<sup>1</sup> at UCT to develop a prototype, CW, Stepped Frequency, Borehole, Tomographic Imaging System, proposed by Dr. Alan Langman, of the University of Cape Town. The system is to demonstrate that a coherent system can be achieved using DDS technology. Most current borehole radar systems pulse a resonant, damped antenna to achieve ultra wide band (UWB) operation<sup>2</sup>. The Geosonde system developed by Mason at Oxford and Sydney covers the band 20 to 80MHz<sup>3</sup>. A stepped frequency system is a more flexible approach, possibly allowing for more efficient, automatically tuned antenna structures. In addition, a coherent system allows for easy extraction of signal phase<sup>4</sup>.

The following user requirements were identified:

- 1. A prototype CW Stepped Frequency transceiver is to be designed.

- 2. The system must transmit in the frequency range: 500kHz 5MHz.

- 3. The transmit power should be no more than 10dBm.

- 4. The system must utilise DDS, or Direct Digital Synthesis technology for the synthesisers.

<sup>&</sup>lt;sup>1</sup>This Group is headed by Prof. M. R. Inggs, and is part of the Electrical Engineering Dept.

<sup>&</sup>lt;sup>2</sup>Information supplied by Prof. Iain Mason.

<sup>&</sup>lt;sup>3</sup>Information supplied by Prof. M. R. Inggs.

<sup>&</sup>lt;sup>4</sup>Information supplied by Prof. M.R. Inggs.

- 5. The transmit, and receive modules need to operate in 47mm diameter boreholes to conform to drilling practice.

- 6. The system must be coherent.

#### 1.2 Outline of dissertation

The dissertation consists of 7 main chapters of discussion:

- 1. The Introduction, which gives the background, and the outline of the dissertation.

- 2. A brief introduction into Cross-Borehole Tomography, and the image reconstruction techniques that are used in this process.

- 3. The reviewing of the physical model of the Radon Transform.

- 4. A simulation of the Borehole Tomographic process.

- 5. The final design.

- 6. Test analysis of the design.

- 7. Conclusions, and recommendations based on the findings, and investigations within the dissertation.

#### 1.2.1 Introduction

The first chapter explains the background behind the dissertation, and gives a short, but detailed summary of each of the main chapters of the dissertation.

### 1.2.2 Cross-Borehole Tomography

The second chapter explains the principle behind Cross-Borehole Tomography, and looks a little deeper into the procedure involved [11, page 2]. The procedure involves placing a transmitter, and a receiver in two different boreholes, and moving them to different positions. At each position the receiver captures the phase, and the

amplitude information [11, 5, page 3]. This information is used in an inverse process which results in image reconstruction of the subsurface [2].

This chapter discusses the environmental factors that need to be considered, when designing a subsurface system [3], [5], [13]: Clay rich sediments within the borehole can absorb the radar energy making propagation through the subsurface impossible [3, page 11]. The use of low transmit frequencies are required to propagate through the subsurface [5, page 3]. The system needs to be low powered due to the explosive hazard of gases present within the subsurface. The quality of the measurements taken at the receiver are severly limited by borehole geometry [3, page 10]. The high temperatures within the borehole require some sort of cooling process for the electronic hardware [5, page 7].

The Radon Transform is defined. This transform forms the basis of all Tomography [1, page 12, (2.5)].

This chapter explains three possible image reconstruction techniques that can be used: Projection-Slice Theorem [2, page 202], Backprojection [2, page 205], and Iterative Methods [11, page 2]. The University of Sydney utilises the Iterative Methods technique when performing image reconstruction, which essentially involves solving a system of linear equations [11].

### 1.2.3 Physical Model of the Radon Transform

The third chapter reviews the physical model of the Radon Transform concerning bulk attenuation, and traveltime for both the continuous case, and the discrete case [1], [11], [13], [14]. This physical model gives us an understanding of the mathematical process involved. The reviewing yields an interesting result: the physical model is derived from the electric field.

This chapter shows that the electrical properties situated in the subsurface (permittivity, and conductivity) effect the amplitude, velocity, and phase of the EM wave that travels through. This is the reason that an image can be obtained. This image is a spatial distribution of the permittivity, and conductivity of the media, which is mapped by the attenuation, and the velocity of the EM wave [2, page 1].

It is also shown mathematically that the traveltime is derived from the phase, and that by utilising a stepped frequency system, the problem of phase ambiguities can be solved. Finally, this chapter reviews the discrete physical model of the Radon Transform concerning phase, and utilising a stepped frequency approach.

#### 1.2.4 Simulation

The fourth chapter investigates a Cross-Borehole Tomographic Imaging simulation, based on the discrete physical model of the Radon Transform covered in chapter 3. The entire process is simulated in Matlab. The phase, and the amplitude are extracted by utilising IF sampling and then IQ demodulation using an easy to implement coherent demodulation technique [50, page 8]. The image reconstruction is based on the Singular Value Decomposition technique [20].

This simulation played an important part in determining the ADC resolution, LNA gain, and the frequency step size utilised for a given medium. The ADC resolution utilised is 12 bit, because this yields a better quality of image reconstruction for both the velocity, and attenuation maps compared to an ADC with 8 bit resolution. A LNA with sufficient gain is needed in order to operate in both dry, and moist earth conditions. The frequency step size utilised needs to be 2MHz or smaller, because this yields an unambiguous path length of 50 metres or greater, while displaying high quality image reconstruction. The unambiguous path length needs to be greater than 35.355 metres, which is the greatest path length in the simulated borehole geometry.

An explanation of Tomographic resolution is also given. The Tomographic resolution is determined by the number of receive positions in the borehole, and the number of pixels utilised in the imaging region. The greater the number of receive positions, and pixels utilised, the better the quality of the reconstructed image.

The simulation compares the use of phase to the use of amplitude. An interesting result is yielded: phase is more accurate than amplitude when it comes to image reconstruction. This result can be clearly understood by looking at the error analysis involved. Once again, the benefit of utilising phase instead of amplitude allows the system to operate with a lower ADC resolution. The velocity reconstruction process became distorted when the phase error was greater than 0.4 degrees.

### 1.2.5 Final Design

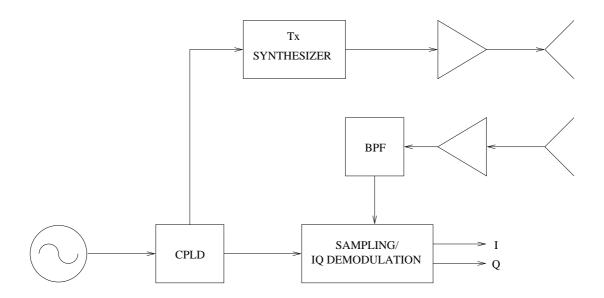

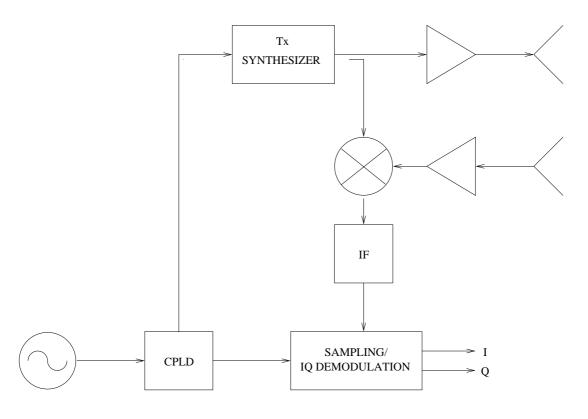

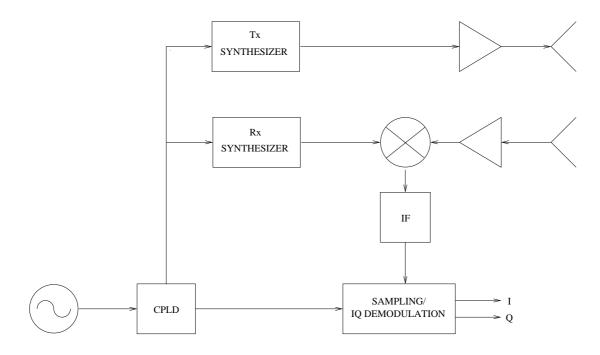

The fifth chapter covers the final design of the system. It briefly discusses three possible architectures: heterodyne, homodyne, and RF Sampling. The heterodyne system is utilised, mainly because the homodyne, and RF Sampling architectures

have problems associated with harmonics within the frequency band of interest [16, page 18, 19, and 20]. The heterodyne system is also compact, and it is desirable to have a compact system which can be utilised in 47mm diameter boreholes in order to meet the demands of the user requirements statement<sup>5</sup>.

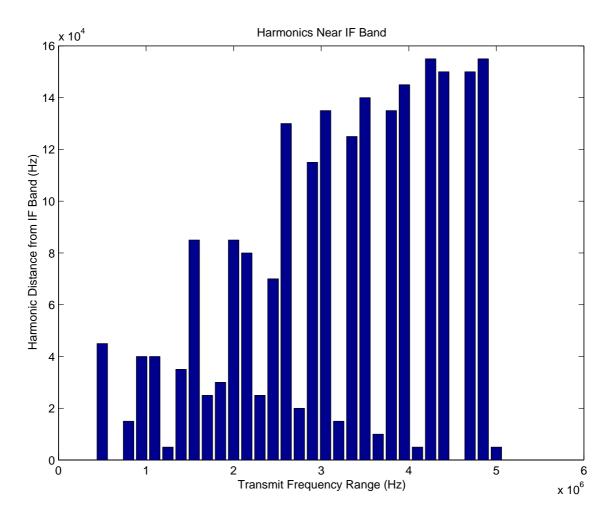

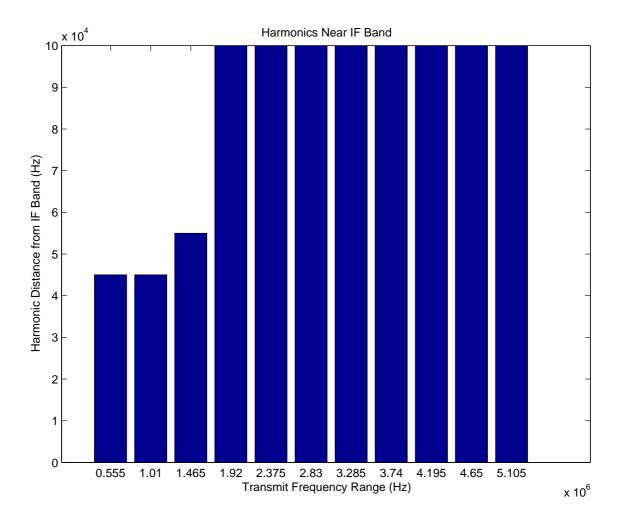

The system specifications are determined by the user requirements for the dissertation, general mathematical analysis of receiver systems, the results of the Matlab simulation covered in the fourth chapter, and other simulations. The IF bandwidth is 455kHz [25]. The system will operate in the transmit frequency range of 500kHz to 5MHz, as specified by the user requirements statement<sup>6</sup>. The frequency step size is 455kHz in order to satisfy the unambiguous path length requirement mentioned in chapter 4, and to ensure the IF remains harmonic free<sup>7</sup>. The BPF, or receiver bandwidth is 21kHz, which will eliminate the effect of the harmonic ±45kHz away from the IF band [25].

The master clock frequency is 58.24MHz, which is a multiple of the IF frequency, and the sampling frequency [16, page 29]. The ADC will undersample the IF signal at 202.222kHz, which results in a cost effective ADC [27]. The clock to the microcontroller is 4.608MHz, which results in zero baud rate error at 2400bps, according to the baud rate simulation.

The transmit power is  $9.9 dBm \approx 10 dBm$ , as specified by the user requirements statement. The ADC has a dynamic range of 72 dB, which meets the requirements mentioned in chapter 4. The maximum LNA gain is 40 dB in order to satisfy the requirement of the simulated gain mentioned in chapter 4.

The receiver dynamic range is 110.96dB. The receiver dynamic range is fairly large, but this is the ideal dynamic range, and in the real world the dynamic range is likely to be lower than 100dB<sup>8</sup>. The compression-free dynamic range assumes that the receiver only has a single signal at the input, and that it is a desired signal [46, page 1]. It does not take into account interfering signals that are likely to lower the overall dynamic range [46, page 1].

The entire system consumes a maximum power of 6.9W when run on  $\pm 5$  volts<sup>9</sup>. The system will operate in the temperature range of  $0^{\circ}$ C to  $70^{\circ}$ C [24], [26], [27], [28], [29], [32], [33], [34], [35], [37], [39], [40], [41], [42].

<sup>&</sup>lt;sup>5</sup>Refer to section 1.1.

<sup>&</sup>lt;sup>6</sup>Refer to section 1.1.

$<sup>^7</sup>$ Refer to section 5.3.2.

<sup>&</sup>lt;sup>8</sup>Information supplied by RF Design Engineer, Paul Fourie, from Reutech Radar Systems.

<sup>&</sup>lt;sup>9</sup>Refer to Table 5.3.

The Control Module, Transmit Module, and Receive Module PCB dimensions are 152mm x 70mm, 203mm x 25mm, and 230mm x 29mm, respectively. The Control Module is not limited by size, but the Transmit Module, and Receive Module are required to operate in the 47mm diameter boreholes, as mentioned in the user requirements statement.

The fifth chapter covers the hardware, and the software implementation. The hardware is implemented by four modules: Control Module, Transmit Module, Receive Module, and the PC Module. The software is explained in detail by the flow diagrams in Appendix C.

Finally, this chapter explains the idea behind coherency, and how to implement the system's coherent control. It is important that the reference clock to both the synthesisers be phase-locked with each other in order to establish a frequency to frequency coherent system. The synthesisers need to be reset in order to place the synthesisers in the same phase, and state [24, page 5, and 11]. The frequency update signal must be synchronised with the reference clock, sample clock, and the synthesiser system clock frequency must be a multiple of the IF frequency, as explained in section 5.5. The sampling must take place on the sample clock, as shown in Figure 5.9.

### 1.2.6 Design and Test Analysis

The sixth chapter involves the test analysis of the final design. It concentrates on the following areas of testing: the compression-free receiver dynamic range, transmitter power, LNA gain, BPF harmonics, and ADC harmonics. Finally, this chapter tests the overall system coherency.

The compression-free receiver dynamic range is measured to be 55.06dB, which is 55.9dB less than the ideal calculated value in section 5.3.7. There also appears to be coupling of the 58.24MHz synthesiser clock signal, and the 9.2MHz harmonic of the 4.608MHz microcontroller clock frequency onto the LNA input<sup>10</sup>. This is caused by the auto-routing of the boards due to time-constraints.

The transmitter power is measured to be within the user-requirements 10dBm<sup>11</sup> value for the entire transmit frequency range. The measured LNA gain corresponds to the programmed LNA gain. However, when the gain is set to 40dB the output

<sup>&</sup>lt;sup>10</sup>Refer to section 6.2.

<sup>&</sup>lt;sup>11</sup>Refer to section 1.1.

signal becomes distorted due to the above mentioned coupling.

The analysis of the BPF output, and input ADC harmonics shows that there is coupling of the above mentioned clock signals, including the 9.707MHz system clock signal. There is local oscillator feedthrough appearing. However, there is good suppression of the coupled clock signals from the IF signal at the ADC input. The 9.707MHz, 4.608MHz, 9.2MHz, and 58.24MHz clock signals are 45.5dB, 49.5dB, 44.5dB, and 41.5dB lower than the required IF signal, respectively. The local oscillator feedthrough is 28dB lower that the required IF signal. The oscilloscope shows that the ADC input IF signal appears to be fairly clean for the entire transmit frequency range.

Finally, the frequency to frequency coherency test for the entire transmit frequency range showed that the system is indeed frequency to frequency coherent<sup>12</sup>. The transmit frequencies, 1.465MHz, 2.375MHz, 3.285MHz, 4.65MHz, and 5.105MHz, all have a change in phase error of less than, or equal to 0.4 degrees, and are therefore, within the desired accuracy in order to reconstruct a high quality velocity map image<sup>13</sup>. However, the transmit frequencies, 555kHz, 1.01MHz, 1.92MHz, 2.83MHz, and 3.74MHz, will have a change in phase error that will not always be less than or equal to 0.4 degrees, and hence, distortion of the reconstructed velocity map image can occur.

The utilisation of a 12 bit ADC should yield a maximum phase error of 0.027 degrees, as mentioned in section 4.7.2. However, the actual phase error is greater than this. This is probably due to inefficient PCB routing, and supply bypassing around the ADC, and the rest of the system<sup>14</sup> [27, page 15].

#### 1.2.7 Conclusions and Recommendations

The final, and seventh chapter gives the conclusions, and the recommendations based on the findings, and investigations within the dissertation. The following main conclusions are drawn:

• The phase yields a better quality of image reconstruction than amplitude, and hence a coherent system is a good choice. The use of phase allows for a lower system ADC Resolution, as proven in section 4.7.2.

<sup>&</sup>lt;sup>12</sup>Refer to section 6.6.

$<sup>^{13}</sup>$ Refer to section 4.7.2.

<sup>&</sup>lt;sup>14</sup>Refer to section 6.2.

- A heterodyne system is the system of choice, because harmonics are factored out of the equation due to the BPF bandwidth, and the choice of transmit frequencies [16, page 18, 19, and 20].

- No error checking is performed on the protocol used in the software, as mentioned in section 5.4.1. Therefore, error in data transmission can occur.

- The system's compression-free dynamic range, LNA gain, BPF output, and ADC input are all being effected by the undesirable coupling of the 58.24MHz synthesiser clock signal, the 9.707MHz system clock signal, and the 4.608MHz crystal frequency for the microcontroller, with its 9.2MHz harmonic<sup>15</sup>. The BPF output, and the ADC input are also experiencing local oscillator feedthrough, as mentioned in section 6.5. The local oscillator is being fed through, because the output signal of the mixer is relatively small ( $\leq -6dBm$ ) in amplitude, and therefore, the BPF (optimum input  $\geq 0dBm$ ) has no effect [25, page 6], [36, page 56].

- The system is frequency to frequency coherent for the entire transmit frequency range, which satisfies the main aim of this dissertation<sup>16</sup>.

- Finally, the system satisfies all the requirements of the user requirements statement covered in section 1.1.

#### The following main recommendations can be made:

- 1. The software protocol must incorporate error checking in the future to guarantee the arrival of the data message. This will prevent timing problems from occuring if a faster PC is utilised. A suggested protocol to use is TCP, or transmission control protocol [49, page 78].

- 2. The next prototype must utilise proper RF PCB routing methods, and must incorporate a power, and ground plane in order to eliminate the coupling of the above mentioned clock signals [47, page 455]. This will help to lower the noise floor, and therefore, improve the system compression-free dynamic range<sup>17</sup>. The introduction of a ground plane helps to eliminate, or reduce any potential difference in the grounds between the ADC, and the rest of the analogue circuitry, which will appear as an error voltage in series with the

<sup>&</sup>lt;sup>15</sup>Refer to sections 6.2, 6.4, and 6.5.

<sup>&</sup>lt;sup>16</sup>Refer to section 6.6.

<sup>&</sup>lt;sup>17</sup>Refer to equation 5.1.

ADC analog input signal [27, page 15]. This will improve the overall change in phase accuracy.

- 3. The IF amplifier must be placed after the mixer, and the BPF must be placed after the the IF amplifier. This will ensure that the BPF attenuates the local oscillator feedthrough effectively [25, page 6].

- 4. The current system must utilise coherent integration in order to improve the change in phase accuracy, so that the error is less than or equal to 0.4 degrees<sup>18</sup> [18, page 144]. This will ensure that the velocity map image can be reconstructed without distortion occurring.

- 5. Finally, a fully-functional system that can be used in the field should be designed. This involves designing the transmit, and receive antenna. Special emphasis must be placed on the fibre optics involved, because the cables can become snagged, and break loose in the borehole.<sup>19</sup>

$<sup>^{18}</sup>$ Refer to section 4.7.2, and 6.6.

<sup>&</sup>lt;sup>19</sup>Information supplied by Prof. Iain Mason.

# Chapter 2

# Cross-Borehole Tomography

### 2.1 Introduction

This chapter, briefly, discusses the Cross-Borehole Electromagnetic Imaging technique. The technique's advantages, uses, and the implementation are mainly discussed.

The environmental factors that effect the propagation of the EM waves are looked at in detail. A Tomographic image is defined.

Finally, the Radon Transform, which forms the basis of all tomography is defined, and three image reconstruction techniques are investigated: Projection-Slice Theorem, Backprojection, and Iterative Methods.

### 2.2 Cross-Borehole Electromagnetic Imaging

There are many techniques which can be used to implement Borehole Tomography. For example, there is Electrical Resistance Tomography, which images the resistivity of the subsurface image. Electrical Resistance Tomography has an advantage over electromagnetic imaging in that fewer boreholes are required [4]. This dissertation will use the technique called Cross-Borehole Electromagnetic Imaging [11, page 2].

This process produces an image of the attenuation or the velocity of the electromagnetic waves sent through the subsurface [11, page 1]. This technique results in fast performance, large area coverage, and its implementation is inexpensive [7],

[10]. This method has been widely used for non-invasive detection of underground metallic and chemical waste forms, such as chromium [10].

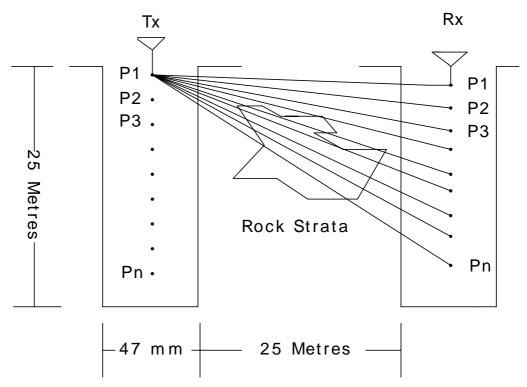

The cross-borehole process can be seen in Figure 2.1. The transmitter is placed in position P1 while the receiver is moved from P1 to Pn. The transmitter is then moved to P2 and the receiver is moved from P1 to Pn again. This process is repeated until the transmitter has covered every position. At each position, the receiver captures the phase (traveltime) or amplitude information [11], [5, page 3]. The information is used in an inverse process which results in target reconstruction [2].

Figure 2.1: The Cross-Borehole Technique with Dimensions

#### 2.3 Environmental Factors

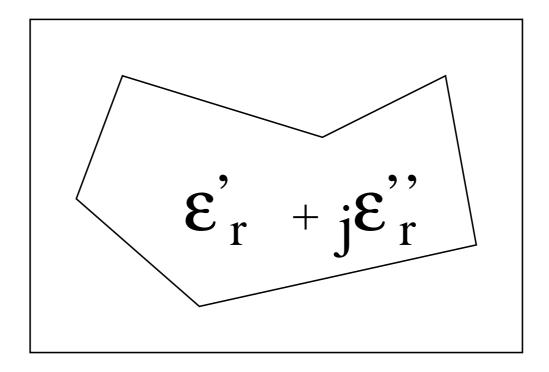

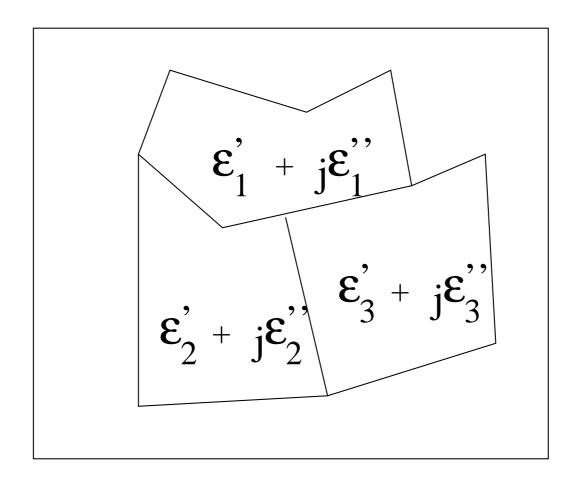

Tomographic images are mappings of the permittivity and conductivity of the target media, which are related to the attenuation and the velocity of the EM wave [2, page 1]. The following properties of the media effect the propagation of the EM waves and gives important information towards the system design:

1. The dielectric constant or relative permittivity of the subsurface material, for

example, water has a higher dielectric constant than air. The imaginary part of the dielectric constant or the loss tangent will effect the attenuation of the wave and the real part of the permittivity will effect the velocity of the wave [13, page 30]. The presence of small amounts of clay-rich sediments in drilling fluids can have the effect of absorbing all the radar energy, and hence, propagation through the subsurface would be impossible [3, page 11].

- 2. Low frequencies need to be used, because the propagation distance through-the-earth for high frequencies is severly limited [5, page 3]. Operating at high frequencies means that the attenuation depends on the conductivity as well as the permittivity of the medium, but at lower frequencies attenuation is independent of permittivity and dependent on conductivity which accounts for ionic losses/conductivity losses [5, page 3].

- 3. The system needs to be low-powered, because of the possible explosive hazard of gases situated in the subsurface<sup>1</sup>. Therefore, an issue of safety needs to be considered.

- 4. The borehole results obtained are severly limited by the hole geometry. The deeper the borehole the greater the ray coverage, and hence, the better the quality of the radar measurements [3, page 10].

- 5. Hardware enclosures electronics will be placed in the borehole which means that the components must be able to withstand the extreme temperatures and the moisture in the boreholes. For example, watertight bakelite containers filled with transformer oil can be used to dissipate the heat so that the electronics can survive under extreme temperature conditions [5, page 7].

## 2.4 Image Reconstruction Techniques

In order to obtain an image of the attenuation or velocity of the EM wave through the medium requires first obtaining various profiles, at different angles, of the image medium. Radar imaging is very similar to tomographic imaging except that instead of considering profiles one considers range [2, page 201]. There is a well defined transform which forms the basis of the process tomography. This transform is called

<sup>&</sup>lt;sup>1</sup>Information supplied by Dr. Alan Langman.

the Radon Transform and can be found in Dean's book [1, page 12, (2.5)].

$$P(\rho, \phi) = \int_{L} \mu(x, y) ds \tag{2.1}$$

Equation 2.1 represents the Radon Transform and is nothing more than the line integral of the spatial distribution of the physical property that is used for imaging,  $\mu(x,y)$ , which gives rise to the various profiles,  $P(\rho,\phi)$ , at different angles,  $\phi$ , and lengths,  $\rho$ .

The hardware will obtain the profiles at various different angles. It is important to note that in cross-borehole tomography the projection or profile angles are limited because of the use of vertical boreholes [5, page 3]. The profiles are obtained by either using the phase (traveltime) or amplitude information at the receiver [11, page 2]. Many projections need to be obtained in order to get a fairly complete image of the spatial distribution of the physical property (wave attenuation or velocity) in question.

The image can be obtained by using software that contains an image reconstruction technique. The software at the University of Sydney, uses the Iterative Methods technique [11]. There are quite a few methods that can be used, but the methods that will be dealt with in this dissertation, briefly, are the following:

- Projection-Slice Theorem or Fourier Reconstruction Technique

- Backprojection

- Iterative Methods

### 2.4.1 Projection-Slice Theorem

This technique relates the one-dimensional Fourier transform of a projection to a central section or slice of the two-dimensional Fourier transform of the imaging distribution [2, page 202]. This is a very important result, because it means that if a large number of projections can be obtained then the result is a very good approximation to the two-dimensional Fourier transform of the imaging property using only one-dimensional transforms of the projections. The whole reconstruction process can be summarised as follows [2, page 202]:

1. Fourier transfom each projection.

- 2. Interpolate to fill in missing data due to a finite number of projections.

- 3. Perform the two-dimensional Fourier transform of the results.

#### 2.4.2 Backprojection

This technique obtains an estimate of the image by using the backprojections of the projections or profiles. It is able to obtain an estimate because it sums up all the backprojections from all possible angles. The process may be summarised as follows [2, page 205]:

- 1. Given a projection  $P(\rho, \phi)$  for a specific angle, the backprojection process assigns the value of the projection to all points in the imaging or x,y space which corresponds to a given  $\rho$ .

- 2. The summation image is formed by the superposition of backprojections from all possible angles.

The more profiles or projections obtained the better the quality of the image will be. It turns out that the image formed by this technique is often blurred and hence some sort of filtering process must be used for deblurring.

#### 2.4.3 Iterative Methods

Iterative methods involve solving a system of linear equations. It can be summarised as follows [11, page 2]:

- 1. The image region is divided into a grid of cells through which the individual electromagnetic waves will pass.

- 2. Every cell is given a constant attenuation value or velocity value ( $\alpha$ ), each wave has a measured attenuation value at the receiver or phase (traveltime) and a certain length through each cell.

- 3. Therefore, every wave forms an equation in the unknown  $\alpha$ .

- 4. The set of equations are solved by iterative methods to determine the unknowns.

This method assumes straight line propagation [11, page 2]. This means multipath effects are ignored. In order to deal with the diffraction of the wave in the subsurface a process called Diffraction Tomography could also be employed [6].

### 2.5 Conclusion

In conclusion, the Cross-Borehole Electromagnetic Imaging technique is fast to implement, and relatively inexpensive.

The environmental factors give important information towards the final system design. The system requires a low transmit frequency range in order to propagate through the earth, and needs to be low-powered, because of the possible explosive hazard of gases present within the subsurface. The components must be able to withstand the extreme temperatures, and the moisture in the boreholes.

Finally, hardware needs to be designed that can capture the phase (traveltime), and amplitude information profiles at the receiver. There are quite a few methods that can be used to implement image reconstruction, but this dissertation will utilise the Iterative Methods technique.

# Chapter 3

# Physical Model of the Radon Transform

### 3.1 Introduction

This chapter shows that the physical model of the Radon Transform can be derived by using the E-field of the EM wave transmitted underground, instead of the signal itself. This chapter shows that the electrical properties situated in the subsurface (the permittivity and conductivity) effect the following of the E-field:

- Amplitude

- Velocity

- Phase

It is due to this effect that an image of the subsurface can be obtained. In Section 3.2, the physical model of the Radon Transform for the continuous case is reviewed and in Section 3.3, the same model is reviewed for the discrete case. Finally, the discrete physical model of the Radon Transform concerning phase, and utilising a stepped frequency approach is examined.

### 3.2 Continuous Case

The tomographic image (in this case) is a spatial distribution of the permittivity and conductivity of the media, which is mapped by the attenuation and the velocity of the EM wave [2, page 1]. The Radon Transform is given by Equation 3.1 [11, page 1] for the continuous case.

$$d_i = \int_L p(l)dl \tag{3.1}$$

In Equation 3.1, p(l) represents the attenuation or the velocity of the EM wave and  $d_i$  represents the amplitude or traveltime for the  $i_{th}$  raypath. The Physical Model of the Radon Transform can be derived by looking at the E-field of the EM wave. The E-field propagating through a general lossy medium<sup>1</sup> is given by Equation 3.2 [13, page 29].

$$E(z) = E_o \cdot e^{-\alpha z} \cdot e^{-j\beta z} \tag{3.2}$$

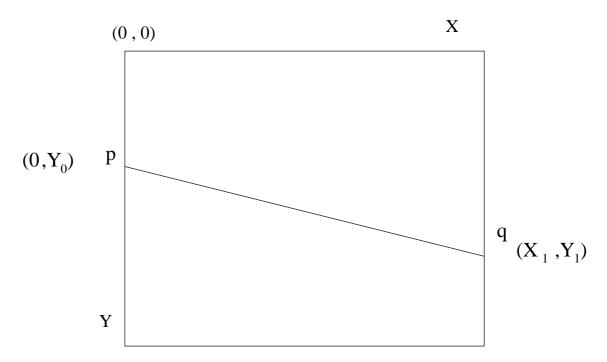

In Equation 3.2,  $\alpha$  is the attenuation constant,  $\beta$  is is the phase constant,  $E_o$  is the initial E-field constant and z is the direction of the propagation. The E-field propagation can be seen in Figure 3.3. The propagation takes place over the path length (p to q) and hence, straight line propagation is assumed. If the co-ordinate system of Figure 3.3 is used and the Z-axis is assumed to be perpendicular to the X and Y axes, then Equation 3.2 can be expressed as follows:

$$E_{pq}(X_1, Y_1) = E_{pq}(0, Y_0) \cdot e^{-\int_L \alpha(X, Y) dS_{pq}} \cdot e^{-j\int_L \beta(X, Y) dS_{pq}}$$

(3.3)

Equation 3.3 represents the E-field as it propagates along the length of the path (L = pq) from the transmitter,  $E_{pq}(0, Y_0)$ , to the receiver,  $E_{pq}(X_1, Y_1)$ , where p = 0 to P and q = 0 to Q<sup>2</sup>. P represents the number of transmit positions and Q represents the number of receive positions. Equation 3.3, as it stands, is not linear and it can be linearized by taking the natural logs of both sides to obtain:

$$-ln\left[\frac{E_{pq}(X_1, Y_1)}{E_{pq}(0, Y_o)}\right] = \int_L \left[\alpha(X, Y) + j\beta(X, Y)\right] dS_{pq}$$

(3.4)

<sup>&</sup>lt;sup>1</sup>See Figure 3.1 for definition

<sup>&</sup>lt;sup>2</sup>Refer to Figure 3.3.

The E-field has the units  $\left[\frac{V}{m}\right]$ . Therefore, the LHS of Equation 3.4 represents the voltage amplitude of the signals. The amplitude of the signals is dependent on the attenuation constant rather than the phase constant and so by taking the real part of Equation 3.4 and replacing the E-field with the voltage amplitudes renders the following equation:

$$-ln\left[\frac{A_{pq}(X_1, Y_1)}{A_{pq}(0, Y_0)}\right] = \int_L \alpha(X, Y) dS_{pq}$$

$$(3.5)$$

Equation 3.5 represents the Radon Transform in terms of the amplitude and the attenuation constant<sup>3</sup>. The phase constant is related to the propagation velocity in the following way [13, page 30]:

$$V(X,Y) = \frac{\omega}{\beta(X,Y)} \tag{3.6}$$

In Equation 3.6, V(X,Y) represents the propagation velocity and  $\omega = 2\pi f$  (f represents the transmit frequency). The Radon Transform in terms of the traveltime and the propagation velocity is as follows [1, page 23]:

$$T_{pq} = \int_{L} \frac{1}{V(X,Y)} dS_{pq} \tag{3.7}$$

The Radon Transform clearly shows that the imaging data (velocity or attenuation) can be related to the information at the receiver (traveltime or amplitude). This means that if the phase measurement is utilized it can be related to the imaging data (phase constant).

In order to obtain the physical model of the Radon Transform a relationship has to be obtained between the imaging data and the electrical properties of the media<sup>4</sup>. The following equations represent this relationship for general lossy media [13, page 30]:

$$\alpha(X,Y) = \omega \cdot \sqrt{\mu(X,Y) \cdot \frac{\epsilon'(X,Y)}{2} \cdot \left[ \sqrt{1 + \left(\frac{\epsilon''(X,Y)}{\epsilon'(X,Y)}\right)^2} - 1 \right]}$$

(3.8)

<sup>&</sup>lt;sup>3</sup>See Equation 3.1

<sup>&</sup>lt;sup>4</sup>See Figure 3.2 for definition

$$V(X,Y) = \frac{1}{\sqrt{\mu(X,Y) \cdot \frac{\epsilon'(X,Y)}{2} \cdot \left[\sqrt{1 + \left(\frac{\epsilon''(X,Y)}{\epsilon'(X,Y)}\right)^2} + 1\right]}}$$

(3.9)

In Equation 3.8 and Equation 3.9,  $\epsilon'(X,Y)$  represents the real part of the permittivity of the media,  $\epsilon''(X,Y)$  represents the imaginary part of the permittivity and  $\mu(X,Y)$  represents the permeability of the media.

The following equations represent the relationship for low-loss media  $(\mu(X,Y) = \mu_o \text{ and loss tangent } = \left(\frac{\epsilon''(X,Y)}{\epsilon'(X,Y)}\right)^2 = \left(\frac{\sigma(X,Y)}{\omega \cdot \epsilon'(X,Y)}\right)^2 \ll 1$ , where  $\sigma(X,Y)$  represents the conductivity of the media) [13, page 31]:

$$\alpha(X,Y) \approx (188.5) \cdot \frac{\sigma(X,Y)}{\sqrt{\epsilon_r(X,Y)}}$$

(3.10)

$$V(X,Y) \approx \frac{c}{\sqrt{\epsilon_r(X,Y)}}$$

(3.11)

In Equation 3.10 and Equation 3.11,  $\epsilon_r(X,Y)$  represents the relative permittivity of the medium and c represents the speed of the electromagnetic wave in free space. The physical model for the Radon Transform (continuous case) has now been derived and now a discrete version (for our purposes) may be obtained from the continuous case.

#### 3.3 Discrete Case

The discrete version of the Radon Transform is given by Equation [11, page 2]:

$$d_i = \sum_{j=1}^{M} p_j \cdot l_{ij} (i = 1....N)$$

(3.12)

In Equation 3.12,  $d_i$  represents the amplitude or traveltime for the  $i_{th}$  raypath,  $p_j$  represents the attenuation or the velocity for pixel j,  $l_{ij}$  is the length of the  $i_{th}$  ray that passes the  $j_{th}$  pixel, M represents the total number of pixels and N represents the total number of rays. This discrete Radon Transform is derived by using the co-ordinate system of Figure 3.4 and transforming Equation 3.3 of Section 3.2 in to

Figure 3.1: Definition of Medium

Figure 3.2: Definition of Media

Figure 3.3: Continuous Propagation of the E-Field

i

0 5 1 2 3 4 m 0 1 2 [0,j] p 4 5 j q  $[i_f, j_f]$ m

Figure 3.4: Discrete Propagation of the E-Field

its discrete form by using definition 14.6 [14, page 856]:

$$E_{pq}[i_f, j_f] = E_{pq}[0, j] \cdot e^{-\sum_{i=0}^{m} \sum_{j=0}^{m} \alpha[i, j] \cdot \triangle S[i, j]_{pq}} \cdot e^{-j\sum_{i=0}^{m} \sum_{j=0}^{m} \beta[i, j] \cdot \triangle S[i, j]_{pq}}$$

(3.13)

In Equation 3.13,  $\alpha[i,j]$  represents the attenuation constant for pixel [i,j],  $\beta[i,j]$  represents the phase constant for pixel [i,j],  $\Delta S[i,j]_{pq}$  represents the length of the ray pq through pixel [i,j] (assumes that the limit of the maximum length  $\rightarrow 0$  from definition 14.6 [14, page 856]) and m represents the number of i columns and j rows (the rows and columns are assumed to be the same for simplification). Taking the natural logs of both sides of Equation 3.13 and using the same assumptions for the continuous case renders the following equation:

$$-ln\left[\frac{A_{pq}[if,jf]}{A_{pq}[0,j]}\right] = \sum_{i=0}^{m} \sum_{j=0}^{m} \alpha[i,j] \cdot \triangle S[i,j]_{pq}$$

$$(3.14)$$

Equation 3.14 represents the discrete Radon Transform in terms of the amplitude and attenuation constants<sup>5</sup>. The discrete Radon Transform concerning traveltime and propagation velocity may be obtained by converting Equation 3.7 in to its discrete form by using definition 14.6 [14, page 856] and using the co-ordinate system of Figure 3.4:

$$T_{pq} = \sum_{i=0}^{m} \sum_{j=0}^{m} \frac{1}{V[i,j]} \cdot \triangle S[i,j]_{pq}$$

(3.15)

The discrete physical model is obtained in the same manner as the continuous case and so converting Equations 3.8, 3.9, 3.10 and 3.11 in to the discrete case renders the following equations for general lossy media and low-loss media:

$$\alpha[i,j] = \omega \cdot \sqrt{\mu[i,j] \cdot \frac{\epsilon'[i,j]}{2} \cdot \left[ \sqrt{1 + \left(\frac{\epsilon''[i,j]}{\epsilon'[i,j]}\right)^2} - 1 \right]}$$

(3.16)

$$V[i,j] = \frac{1}{\sqrt{\mu[i,j] \cdot \frac{\epsilon'[i,j]}{2} \cdot \left[\sqrt{1 + \left(\frac{\epsilon''[i,j]}{\epsilon'[i,j]}\right)^2 + 1\right]}}$$

(3.17)

<sup>&</sup>lt;sup>5</sup>See Equation 3.12

$$\alpha[i,j] \approx (188.5) \cdot \frac{\sigma[i,j]}{\sqrt{\epsilon_r[i,j]}}$$

(3.18)

$$V[i,j] \approx \frac{c}{\sqrt{\epsilon_r[i,j]}} \tag{3.19}$$

Therefore, the physical model of the Radon Transform for the discrete case has been derived. It should be noted that at this point in time the model does not take in to account the stepped frequency capability or the phase as a measurement.

Equation 3.15 concerns itself with the traveltime, but the system under design will capture phase measurements, and extract the traveltime from the captured phase measurements. In fact, it turns out that by measuring the phase directly, and then extracting the traveltime is much more efficient than measuring the traveltime directly<sup>6</sup>. It is important to note that the measured phase signal can only take on values in a  $2\pi$  range, while the true phase signal can take on any value, and hence, create phase ambiguities. This is known as phase wrapping [51]. The phase will need to be unwrapped in order to extract the true traveltime, as discussed below.

This implies that the change in phase must be related to the traveltime. This is proved by the following equations [17, page 104]:

$$\beta = k = \frac{2\pi}{\lambda} \tag{3.20}$$

$$\lambda = \frac{\nu}{f} \tag{3.21}$$

$$L = \nu \cdot T_{pq} \tag{3.22}$$

In equation 3.20,  $\beta$  represents the phase constant, or the angular wave number of the travelling waveform, and  $\lambda$  represents the wavelength of the travelling waveform. In equation 3.21, v represents the velocity of the travelling wave, and f represents the frequency of the travelling wave. In equation 3.22, L represents the total distance the travelling wave has travelled in metres, and  $T_{pq}$  represents the travelline of the travelling wave along ray path  $pq^7$ . The units of  $\beta$  are  $\frac{\phi}{m}$ , where  $\phi$  represents the

<sup>&</sup>lt;sup>6</sup>Information supplied by Dr. Alan Langman

<sup>&</sup>lt;sup>7</sup>See equation 3.15

phase (rads) of the travelling wavefom, and m represents the length in metres. In order to derive the  $\Delta \phi$  (change in phase), equation 3.20 will have to be multiplied by equation 3.22. The result is the following equation:

$$\Delta \phi = 2\pi \cdot f \cdot T_{pq} = \omega \cdot T_{pq} \tag{3.23}$$

Equation 3.23 clearly shows that the traveltime is related to the change in phase by a factor of  $\omega$ , which represents the angular frequency. Equation 3.23 at this time does not take in to account unambiguous phase, because it is phase wrapped as mentioned above. This means that equation 3.23 is only valid if the total change in phase is less than or equal to  $2\pi$  [18, page 84]. This implies that the transmitter needs to transmit at a frequency that has a wavelength greater than the distance between the two boreholes to ensure that the change in phase is less than  $2\pi$ . The ambiguous phase problem can be solved by using a stepped frequency approach [18, page 84]. In order for the unambiguous phase to be taken into account, a new factor needs to be added to equation 3.23 to yield the following final equations:

$$\Delta \phi_x + 2\pi n_x = 2\pi \cdot f_x \cdot T_{nq} (n_x = 0, 1, 2...\infty; x = 1, 2...X)$$

(3.24)

$$T_{pq} = \frac{\Delta \phi_x + 2\pi n_x}{2\pi \cdot f_x} (n_x = 0, 1, 2...\infty; x = 1, 2...X)$$

(3.25)

In equation 3.24, and 3.25, factor  $2\pi n_x$  accounts for the fact that multiple cycles or phase shifts of  $2\pi$  radians have resulted where  $n_x$  represents the number of complete transmit cycles that have occurred when sampling begins at the receiver. The factor  $f_x$  accounts for a stepped frequency situation, and X represents the total number of transmit frequencies.

The discrete physical model of the Radon Transform concerning phase may be obtained by substituting Equation 3.15 into equation 3.24 or 3.25 and using the coordinate system of Figure 3.4. Equation 3.25 cannot be solved without using a stepped frequency approach, since if only one transmit frequency is used then there would be two unknowns ( $T_{pq}$  and  $n_x$ ), and in order to solve the two unknowns at least two equations are needed [19]. However, if we use two or more transmit frequencies travelling along the same ray path pq the traveltime must be the same for both or more frequencies, since traveltime is dependent on the velocity of the

travelling wave, and the travel distance of the wave<sup>8</sup>. The velocity is in turn dependent on the permittivity, and this will not change along the same ray path  $pq^9$ . The length along the ray path will stay the same. Hence, the fact that the traveltime is the same for two or more transmit frequencies means that equation 3.25 can be equated with itself to yield the following equation:

$$\frac{\Delta\phi_1 + 2\pi n_1}{2\pi \cdot f_1} = \frac{\Delta\phi_2 + 2\pi n_2}{2\pi \cdot f_2} = \frac{\Delta\phi_x + 2\pi n_x}{2\pi \cdot f_x}$$

(3.26)

$$(n_x = 0, 1, 2...\infty; x = 1, 2...X)$$

The only unknowns now are  $n_1$  and  $n_2$ ,  $\Delta \phi_1$  and  $\Delta \phi_2$  are captured by the receiver. It is just a question of substituting integer values for these two unknowns until the equations are equivalent. Once this occurs, then the traveltime  $(T_{pq})$  is known, and hence, the phase is correctly unwrapped.

### 3.4 Conclusion

In conclusion, the physical model of the Radon Transform is derived from the electric field. The Radon Transform clearly shows that the velocity and the attenuation of the EM wave propagating through the image medium can be related to the phase (traveltime) and bulk amplitude at the receiver, respectively.

The measured phase at the receiver is phase wrapped, and hence, phase ambiguities can occur. This phase wrapping places limitations on the transmit frequency range. A stepped frequency system allows for proper phase unwrapping, and hence, the true traveltime can be extracted from the measured phase without limiting the transmit frequency range.

<sup>&</sup>lt;sup>8</sup>See equation 3.22

<sup>&</sup>lt;sup>9</sup>See equation 3.17, and 3.19

# Chapter 4

## Simulation

### 4.1 Introduction

The simulation performs the entire Cross-Borehole EM Imaging process<sup>1</sup>. The Tomographic simulation utilises the discrete equations that are reviewed in Chapter 3, especially the traveltime physical model, and the attenuation physical model of the Radon Transform.

This chapter covers the following:

- Explains the simulation procedure by means of a flow diagram located in Appendix B.

- Discusses, and uses the simulation to determine the ADC resolution, LNA gain, and the frequency step size.

- The concept of Tomographic resolution is introduced, and examined.

- Finally, the simulation compares the use of phase to the use of amplitude.

## 4.2 Tomographic Simulation

The simulation is written in Matlab, and the source code may be found on the Borehole Tomography CD<sup>2</sup>. This chapter will only discuss the main findings during

<sup>&</sup>lt;sup>1</sup>Refer to Chapter 2.

<sup>&</sup>lt;sup>2</sup>File location on CD: D:\simulation\Tomo\*.m

the simulation process. If a more detailed understanding is needed please refer to the source code for more information.

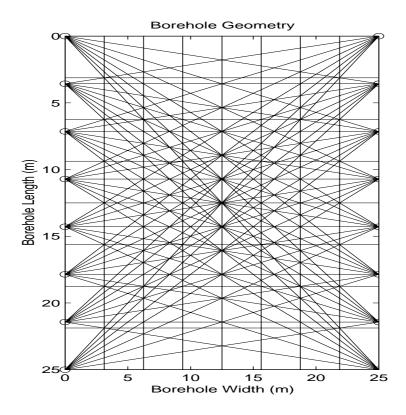

The simulation procedure is illustrated by a flow diagram in Figure B.1, which may be found in Appendix B. The first stage involves plotting the transmit, and receive positions defined by the user input. The second stage involves plotting the pixel area, and the ray paths defined by the user input. The user input is listed with typical values in Table 4.1. A typical borehole geometry generated with the user input values of Table 4.1 is shown in Figure 4.1. The left hand y-axis represents the Tx Position, and the right hand y-axis represents the Rx Position. The length, and width are set at 25 metres (adjustable), because the final system will eventually be tested with this geometry<sup>3</sup>.

Table 4.1: User Input Typical Values

| USER INPUT                    | TYPICAL VALUES |

|-------------------------------|----------------|

| Tx Positions                  | 8              |

| Rx Positions                  | 8              |

| Pixel Size (row)              | 8              |

| Pixel Size (cols)             | 8              |

| Tx Phase (degrees)            | 0              |

| Minimum Tx Frequency (Hz)     | 500000         |

| Maximum Tx Frequency (Hz)     | 5000000        |

| Tx Voltage (V)                | 1              |

| Full-Scale Value of ADC (V)   | 2              |

| Quantization Noise of ADC (V) | 1e-3           |

| ADC Input Voltage (V)         | 2              |

| Frequency Step Size (Hz)      | $\leq 2000000$ |

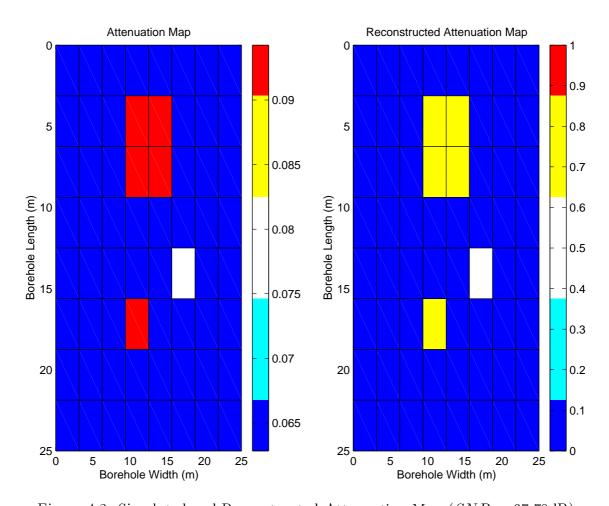

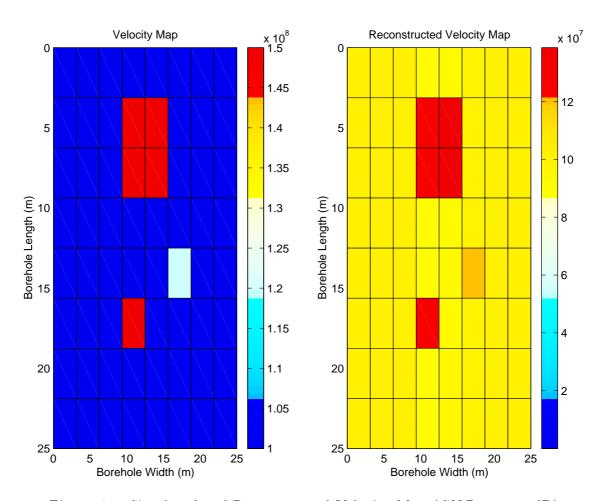

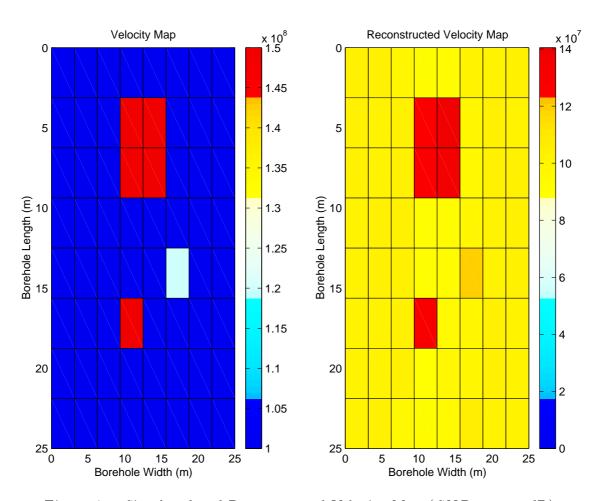

The third, and fourth stages involve plotting the velocity, and attenuation matrices/maps. The simulation assumes that the media is homogenous, low-loss, and non-magnetic in nature. Therefore, equation 3.18, and 3.19 from Chapter 3 were used to calculate the attenuation constants, and the velocity constants, respectively. The conductivity,  $\sigma[i,j]$ , was set at 1e-3  $(\Omega \cdot m)^{-1}$ , which represents the conductivity value for dry earth [15, page 283]. The relative permittivity,  $\epsilon_r[i,j]$ , ranges from 4 to 9, where 9 represents the value for sand [15, page 283]. The simulated attenuation map can be seen on the left hand side of Figure 4.2, and the simulated velocity map can be seen on the left hand side of Figure 4.3. The velocity and attenuation simulated, and reconstructed maps both have shading value scales located on the

<sup>&</sup>lt;sup>3</sup>Information Supplied by Prof. Iain Mason.

Figure 4.1: A Typical Borehole Geometry

right of each map. The attenuation map scale is in Nepers per a metre  $\left[\frac{Np}{m}\right]$ , and the velocity map scale is in metres per a second  $\left[\frac{m}{s}\right]$ .

The fifth stage involves calculating the ray intersection point with the pixels, and hence the ray lengths for each pixel. The sixth stage calculates the overall change in phase, and the bulk attenuation for each ray path length, from the Tx to Rx position. These resulting values will eventually be sampled in the IF sampling stage.

The seventh stage calculates the expected voltage return, and the required LNA gain. The eighth stage determines the ADC resolution, and adds the quantization noise specified by the user input to the ADC signal. The ninth stage performs the IF sampling algorithm [16, page 33, and 34]. The tenth stage extracts the I, and Q samples to determine the phase, and the amplitude. It also extracts the traveltime from the phase.

The eleventh stage reconstructs the simulated velocity, and attenuation map from the extracted traveltime, and amplitude values, respectively, using the Singular Value Decomposition (SVD) technique [20, page 61, and 62]. The twelfth stage performs LSQ error calculations on the phase, and on the SVD technique for both the reconstructed attenuation, and the velocity simulated maps. The error is displayed

Figure 4.2: Simulated and Reconstructed Attenuation Map (SNR = 67.78 dB)

Figure 4.3: Simulated and Reconstructed Velocity Map (SNR=67.78 dB)

in the form of a plot. Finally, the thirteenth stage determines the unambiguous path length.

Stages seven to thirteen are discussed in more detail below.

## 4.3 ADC Resolution

The ADC resolution refers to the number of bits of the ADC. The resolution is determined from the following equation [21, page 122]:

$$SNR = 6.02B + 10.8 - 20log_{10} \left(\frac{X_m}{\sigma_x}\right) \tag{4.1}$$

In equation 4.1, SNR refers to the signal to noise ratio of the ADC, B = N - 1, where N represents the number of bits (ADC resolution),  $X_m$  represents the full-scale amplitude of the A/D converter, and  $\sigma_x$  is the rms value of the signal amplitude at the A/D converter. It is desirable to have  $X_m$  matched to  $\sigma_x^4$ .

The SNR is determined from the following equation [21, page 122]:

$$SNR = 10log_{10} \left( \frac{\sigma_x^2}{\sigma_e^2} \right) \tag{4.2}$$

Equation 4.1 is derived from this equation [21, page 122]. In equation 4.2,  $\sigma_x^2$  represents the signal power, and  $\sigma_e^2$  represents the noise power. This noise power is assumed to have a uniformly distributed probability density function [21, page 121], and therefore can be determined from the following equation [22, page 134]:

$$VAR[X] = \sigma_e^2 = \frac{(b-a)^2}{12}$$

(4.3)

In equation 4.3, b and a represent the upper, and lower bound values for the quantization noise, respectively.

The values from Table 4.1 were substituted into the above equations. The resultant SNR with these substituted values is 67.78dB, and the resultant ADC resolution is 10.97 bits, which rounds off to 12 bits, since 11 bit ADCs are not common. These particular values from Table 4.1 were utilised, because the values led to optimal

<sup>&</sup>lt;sup>4</sup>Refer to section 4.5.

reconstruction of both the velocity, and the attenuation maps during the simulation process<sup>5</sup>.

It is important to note that the ADC does not have to have a 12 bit resolution. It can utilise a lower resolution, and generate the same optimal reconstruction results, as above, by using the method of coherent integration [18, page 144]. This method takes a number of sampled values (phase, and amplitude) at each Rx position, and averages them. If an 8 bit ADC is utilised instead of a 12 bit ADC, then the SNR would drop to 49.9dB. The total number of sampled values, in each Rx position, required to bring the SNR back to 67.78dB, according to the simulation, is 61. This method is not implemented in this dissertation, because this hardware technology is relatively new, and therefore it is easier to establish a proven single sampled value coherent system first. A 12 bit ADC is utilised<sup>6</sup>.

## 4.4 Tomographic Resolution

The radar resolution is dependent on the bandwidth of the transmit signal [23, page 15, and 17]. The radar range resolution refers to the minimum distance that the targets need to be from each other in order to detect two targets [23, page 15]. This explains the term radar resolution, but what is Tomographic resolution? Clearly, Cross-Borehole Tomography does not involve detecting targets, but rather producing subsurface images. Hence, the term Tomographic resolution must refer to the quality of the subsurface images reconstructed, but what effects the quality of these images?

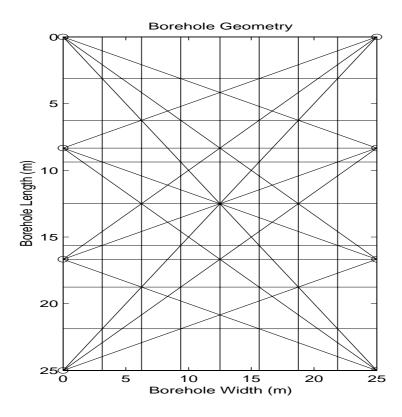

In Figure 4.4, there are four Tx, and Rx positions. In Figure 4.5, there are six Tx, and Rx positions. In Figure 4.5, there are more ray paths, than in Figure 4.4. By looking at the Figures 4.4, and 4.5, it can be seen that if more Tx, and Rx positions are utilised then the area of ray coverage over the desired image region will be greater. Looking at equation 3.14, and 3.15 of Chapter 3, a subsurface image can only be reconstructed if the ray path passes through that part of the image region. In other words, the image region is pixelised, and these pixels each represent an unknown, which needs to be solved<sup>7</sup>. If there is no ray path through a pixel, then that particular unknown is cancelled out, and therefore the reconstructed image will not show that particular area of the image region. Hence, the quality of the

<sup>&</sup>lt;sup>5</sup>Refer to section 4.7.

<sup>&</sup>lt;sup>6</sup>Refer to section 4.7.

<sup>&</sup>lt;sup>7</sup>Refer to Chapter 3.

reconstructed image will be poor. Therefore, the borehole geometry used in Figure 4.5 will result in a better quality reconstructed image than in Figure 4.4, because its geometry utilises more Tx, and Rx Positions, and therefore utilises a greater area of ray coverage.

The number of Tx, and Rx positions is not the only factor that effects the overall quality of the reconstructed subsurface image. In Figure 4.4, the image region is divided into an array of eight by eight pixels. This represents an array of 64 unknowns. In Figure 4.5, the image region is divided into an array of six by six pixels. This represents an array of 36 unknowns. In reality, the image region will be heterogenous in nature, and not homogenous as stated in this simulation. Therefore, the permittivity, and conductivity will vary throughout the image region, and hence the more unknowns (pixels) there are to solve for, the better the quality of the reconstructed image. This can be seen by looking at Figure 4.4, or 4.5. Take any pixel where the ray path passes through, and sub-divide it by a large number. Imagine that within that pixel the permittivity, and conductivity is varied. If a number of unknowns are utilised there is a greater chance of reconstructing this permittivity, and conductivity variance, yielding a better quality reconstructed image.

Figure 4.4: Borehole Geometry with Tx, and Rx Positions = 4

Figure 4.5: Borehole Geometry with Tx, and Rx Positions = 6

### 4.5 LNA Gain

The receiver hardware utilises a LNA<sup>8</sup>. Hence, the overall SNR at the receiver is improved. The LNA requires a gain such that the return signal is amplified to the full-scale range of the ADC [21, page 122]. This can be seen by looking at equation 4.1 in section 4.3. If the signal,  $\sigma_x$ , is too small then the term  $-20log_{10}\left(\frac{X_m}{\sigma_x}\right)$  will become large, and negative, thereby reducing the overall SNR of the ADC [21, page 122]. If the signal,  $\sigma_x$ , is too large then it will exceed the full-scale value of the ADC causing clipping of the signal to occur, and hence the true signal's amplitude will be lost [21, page 122]. However, if  $X_m \approx \sigma_x$  then the above term becomes  $-20log_{10}$  (1), which is equal to zero [14]. This term is cancelled out, and therefore equation 4.1 now has an optimum SNR. Therefore, the LNA gain must be such that the input return signal is amplified, so that  $X_m \approx \sigma_x$ .

The results of the simulation for determining LNA gain can be found in Table 4.2, and Table 4.3. In Table 4.2, the expected LNA gain for the first thirty-two ray path lengths is shown, and Table 4.3 shows the expected LNA gain for the last thirty-two

<sup>&</sup>lt;sup>8</sup>Refer to Chapter 5.

<sup>&</sup>lt;sup>9</sup>All input variables were taken from Table 4.1.

ray path lengths. There are sixty-four ray path lengths in total, because there are eight Tx, and eight Rx positions, as shown in Figure 4.1. These tabulated results show that the maximum LNA gain needs to be around 25.4dB, since Table 4.2, and Table 4.3 both show a maximum gain of 25.32dB.

Bear in mind that this simulation assumes that it is dealing with low-loss, non-magnetic media, and that the media consists of dry earth (sand)<sup>10</sup>. In a real environment the earth is likely to be moist, and the attenuation much greater<sup>11</sup>. Therefore, an LNA with a gain much greater than 25.32dB is needed in order to cater for the effects of the real environment.

## 4.6 Frequency Step Size

This section determines the frequency step size, and will show that the frequency step size is inversely proportional to the unambiguous path length.

The unambiguous path length refers to the ray path length where there are no phase ambiguities, much like unambiguous range in Radar systems [18, page 84]. The unambiguous path length in a non-stepped frequency system would be the length over which the overall phase change was less than, or equal to  $2\pi$  [18, page 84]. This means that the wavelength of the transmit signal would have to be greater, or equal to the distance between the boreholes, and hence, limit the transmit frequency range capability<sup>12</sup>.

The following equation is yielded for the unambiguous path length by looking at the equations for multiple frequency CW RADAR in Hovanessian's book [18, page 84-85], and assuming one way wave travel with the speed of light replaced with the velocity of the EM wave:

$$L_{unambig} = \frac{v}{\triangle f} \tag{4.4}$$

In equation 4.4,  $L_{unambig}$  represents the unambiguous path length,  $\triangle f$  represents the frequency step size, and v represents the velocity of the travelling EM wave<sup>13</sup>. It is clear to see from equation 4.4 that by making the frequency step size smaller

<sup>&</sup>lt;sup>10</sup>Refer to section 4.2.

<sup>&</sup>lt;sup>11</sup>Refer to Chapter 2.

<sup>&</sup>lt;sup>12</sup>Refer to Chapter 3.

<sup>&</sup>lt;sup>13</sup>Refer to Chapter 3.

Table 4.2: Return Values vs LNA Gain (1-32 Ray Path Lengths)

| RETURN VALUES (V) | LNA GAIN (dB) |

|-------------------|---------------|

| 0.20787           | 19.6646       |

| 0.20458           | 19.8031       |

| 0.16749           | 21.5409       |

| 0.14622           | 22.7204       |

| 0.13063           | 23.6995       |

| 0.12313           | 24.2130       |

| 0.11342           | 24.9268       |

| 0.10845           | 25.3161       |

| 0.20458           | 19.8031       |

| 0.17081           | 21.3701       |

| 0.16778           | 21.5260       |

| 0.15915           | 21.9844       |

| 0.15701           | 22.1019       |

| 0.15218           | 22.3735       |

| 0.14232           | 22.9555       |

| 0.12632           | 23.9908       |

| 0.16749           | 21.5409       |

| 0.16778           | 21.5260       |

| 0.17081           | 21.3701       |

| 0.16778           | 21.5260       |

| 0.19521           | 20.2106       |

| 0.17347           | 21.2360       |

| 0.16379           | 21.7351       |